## Radiation Hardended Ultra Low Dropout Fixed Positive Linear Regulator +3.

#### **Product Summary**

| Part Number  | Ι <sub>Ο</sub> | V <sub>IN</sub> | V <sub>OUT</sub> |  |

|--------------|----------------|-----------------|------------------|--|

| IRUH330118BK | 3.0A           | 3.3V            | 1.8V             |  |

| IRUH330118BP | 3.0A           | 0.01            | 1.0 V            |  |

PD-97591B

## (5962F1023503K) IRUH330118BK out IRUH330118BP +3.3V<sub>IN</sub> to +1.8V<sub>OUT</sub> @3.0A

## Description

The IRUH330118 is a space qualified, ultra low dropout linear regulator designed specifically for applications requiring high reliability, low noise and radiation hardness.

#### Features

- Silicon On Insulator (SOI) CMOS Regulator IC, CMOS Latch-Up Immune, Inherently Rad Hard

- Total Dose Capability up to 300Krads(Si) (Condition A); Tested to 500Krad (Si)

- ELDRS up to 100Krad(Si) (Condition D)

- SEU Immune up to LET = 80 MeV\*cm<sup>2</sup>/mg

- Space Level Screened

- Fast Transient Response

- Timed Latch-Off Over-Current Protection

- Internal Thermal Protection

- On/Off Control via Shutdown Pin, Power Sequencing Easily Implemented

- Isolated Hermetic MO-078AA Package Ensures Higher Reliability

- This part is also available in 8 Lead Flat pack Package as IRUH330118AK / RUH330118AP

#### **Absolute Maximum Ratings**

| Parameter                                            | Symbol            | Min. | Max.                  | Units |  |

|------------------------------------------------------|-------------------|------|-----------------------|-------|--|

| Power Dissipation @ T <sub>C</sub> = 125°C           | PD                | -    | 25                    | W     |  |

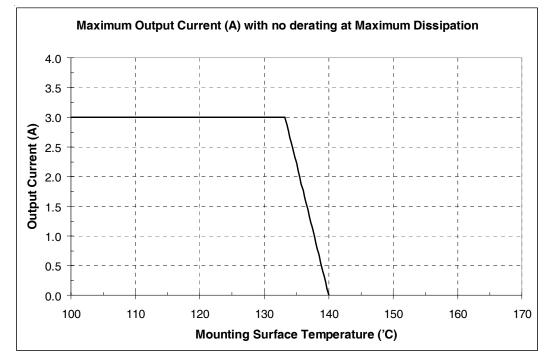

| Maximum Output Current @ Maximum                     |                   | -    | See Fig 4             | А     |  |

| Power Dissipation with no Derating                   | I <sub>O</sub>    |      |                       | A     |  |

| Non-Operating Input Voltage                          | V <sub>IN</sub>   | -0.3 | +8.0                  |       |  |

| Operating Input Voltage                              | V <sub>IN</sub>   | 2.9  | 6.4                   |       |  |

| Ground                                               | GND               | -0.3 | 0.3                   | V     |  |

| Shutdown Pin Voltage                                 | V <sub>SHDN</sub> | -0.3 | V <sub>IN</sub> + 0.3 |       |  |

| Output Pin Voltage                                   | V <sub>OUT</sub>  | -0.3 | V <sub>IN</sub> + 0.3 |       |  |

| Operating Case Temperature Range                     | т <sub>о</sub>    | -55  | +140                  |       |  |

| Storage Temperature Range                            | Τ <sub>S</sub>    | -65  | +150 °C               |       |  |

| Maximmum Junction Temperature                        | Т <sub>Ј</sub>    | -    | +150                  |       |  |

| Lead Temperature (Soldering 10sec)                   | Т                 | -    | +300                  |       |  |

| Pass Transistor Thermal Resistance, Junction to Case | R <sub>THJC</sub> | -    | 1.0                   | °C/W  |  |

## **Electrical Characteristics** ① Pre-Radiation $@T_c = 25^{\circ}C$ , $V_{IN} = 3.3V$ (Unless Otherwise Specified)

| Parameter                                   | Test Conditions                                            | Symbol             | Min.  | Тур. | Max.  | Units |

|---------------------------------------------|------------------------------------------------------------|--------------------|-------|------|-------|-------|

| Output Voltage ①                            | $2.8V \le V_{IN} \le 3.8V$ , 50mA $\le I_{OUT} \le 3.0A$   |                    | 1.773 | 1.8  | 1.827 |       |

|                                             | $2.8V \le V_{IN} \le 3.8V$ , $50mA \le I_{OUT} \le 3.0A$ , |                    | 1.746 | 1.8  | 1.854 | V     |

|                                             | -55°C to +125°C                                            | V <sub>OUT</sub>   | 1.740 | 1.0  | 1.004 |       |

|                                             | $2.8V \le V_{IN} \le 3.8V$ , $50mA \le I_{OUT} \le 3.0A$ , |                    | 1.737 | 1.8  | 1.836 |       |

|                                             | Post -Rad                                                  |                    | 1.707 | 1.0  | 1.000 |       |

| Current Limit                               | Over-Current Latching, -55°C to +125°C,                    | ILATCH             | 3.5   | -    | -     | А     |

|                                             | Post -Rad                                                  | LATON              | 0.0   |      |       |       |

| Over-Current Time-to-Latch                  | IO > ILATCH                                                | t <sub>LATCH</sub> | -     | 10   | -     | ms    |

| Maximum Shutdown Temp. <sup>②</sup>         |                                                            | T <sub>LATCH</sub> | 125   | 140  | -     | °C    |

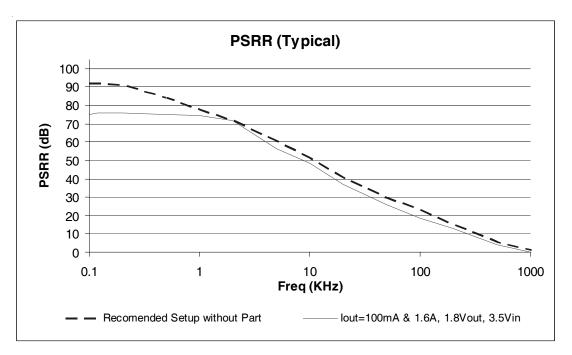

| Ripple Rejection <sup>®</sup>               | F= 120Hz, I <sub>O</sub> = 50mA, -55°C to +125°C           | PSRR               | 65    | -    | -     | dB    |

|                                             | F= 120Hz, I <sub>O</sub> = 50mA, Post -Rad                 |                    | 40    | -    | -     |       |

| V <sub>SENSE</sub> Pin Current <sup>②</sup> | -55°C to +125°C                                            | ISENSE             | -     | 1.6  | -     | mA    |

| Minimum SHDN Pin "On"                       | I <sub>SOURCE</sub> = 200μA, -55°C to +125°C               | N/                 | -     | -    | 0.8   | V     |

| Threshold Voltage                           | Post -Rad                                                  | V <sub>SHDN</sub>  |       |      |       |       |

| Maximum SHDN Pin "Off"                      | I <sub>SOURCE</sub> = 200μA, -55°C to +125°C               | V <sub>SHDN</sub>  | 1.2   | _    | _     | v     |

| Threshold Voltage                           | Post -Rad                                                  | SHDN               | 1.2   | -    | -     | v     |

| Output Voltage at Shutdown                  | R <sub>LOAD</sub> = 36 Ohms, V <sub>SHDN</sub> = 3.3V      | V <sub>OUT</sub>   | -0.1  | -    | 0.1   | v     |

| Output Voltage at Shutdown                  | -55°C to +125°C, Post-Rad                                  |                    |       |      |       |       |

| SHDN Pin Leakage Current ②                  | V <sub>SHDN</sub> = 3.3V, -55°C to +125°C,Post-Rad         | I <sub>SHDN</sub>  | -10   | -    | 10    | μA    |

| SHDN Pin Pull-Up Current ®                  | $V_{SHDN} = 0.4V$                                          |                    | -98   | -    | -56   | μΑ    |

|                                             | V <sub>SHDN</sub> = 0.4V, -55°C to +125°C                  | I <sub>SHDN</sub>  | -140  | -    | -30   |       |

|                                             | V <sub>SHDN</sub> = 0.4V, Post-Rad                         |                    | -98   | -    | -56   |       |

| Power On Reset Threshold 2                  | Sweep V <sub>IN</sub> and Measure Output                   | V <sub>T-POR</sub> | -     | 1.7  | -     | V     |

| Quiescent Current @                         | No Load                                                    |                    | -     | -    | 15    | mA    |

|                                             | Full Load                                                  | lq                 | -     | -    | 90    |       |

#### Notes:

0 Connected as shown in Fig.1 and measured at the junction of V\_{OUT} and V\_{SENSE} Pins. 0 Under normal closed-loop operation. Guaranteed by design. Not tested in production.

## IRUH330118BK IRUH330118BP

## **Radiation Performance Characteristics**

| Test                        | Conditions                              | Min | Тур                | Unit                     |

|-----------------------------|-----------------------------------------|-----|--------------------|--------------------------|

|                             | MIL-STD-883, Method 1019 (Condition A)  |     |                    |                          |

| Total Ionizing Dose (Gamma) | Operating Bias applied during exposure  | 300 | 500 O              | Krads (Si)               |

|                             | Minimum Rated Load, Vin = 6.4V          |     |                    |                          |

|                             | MIL-STD-883, Method 1019 (Condition D)  |     |                    |                          |

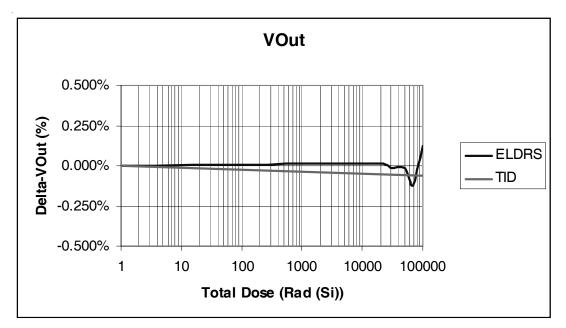

| Total Ionizing Dose (Gamma) | (ELDRS) Operating Bias applied during   | 100 | See ②              | Krads (Si)               |

|                             | exposure Minimum Rated Load, Vin = 6.4V |     |                    |                          |

| Single Event effects        | Heavy lons (LET)                        |     |                    |                          |

| SEU, SEL, SEGR, SEB         | Operating Bias applied during exposure  | 84  |                    | MeV*cm <sup>2</sup> /mg  |

|                             | under varying operating conditions      |     |                    |                          |

| Neutron Fluence             | MIL-STD-883, Method 1017                |     | 1.0e <sup>11</sup> | Neutrons/cm <sup>2</sup> |

#### Notes:

Tested to 500Krad (Si).

<sup>②</sup> See Fig. 5.

## **Space Level Screening Requirements**

| TEST/INSPECTION          | SCREENING LEVEL | MIL-STD-883 |  |  |

|--------------------------|-----------------|-------------|--|--|

|                          | SPACE           | METHOD      |  |  |

| Nondestructive Bond Pull | 100%            | 2023        |  |  |

| Internal Visual          | 100%            | 2017        |  |  |

| Seal                     | 100%            | 1014        |  |  |

| Temperature Cycle        | 100%            | 1010        |  |  |

| Constant Acceleration    | 100%            | 2001        |  |  |

| Mechanical Shock         | 100%            | 2002        |  |  |

| PIND                     | 100%            | 2020        |  |  |

| Pre Burn-In-Electrical   | 100%            |             |  |  |

| Burn-In                  | 100%            | 1015        |  |  |

| Final Electrical         | 100%            |             |  |  |

| Radiographic             | 100%            | 2012        |  |  |

| External Visual          | 100%            | 2009        |  |  |

## IRUH330118BK IRUH330118BP

International

#### **Application Information**

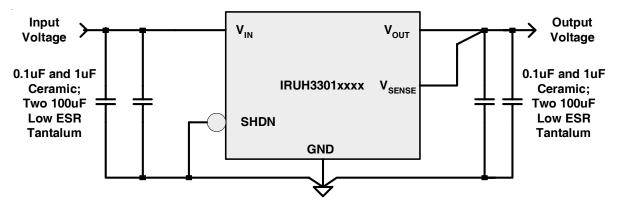

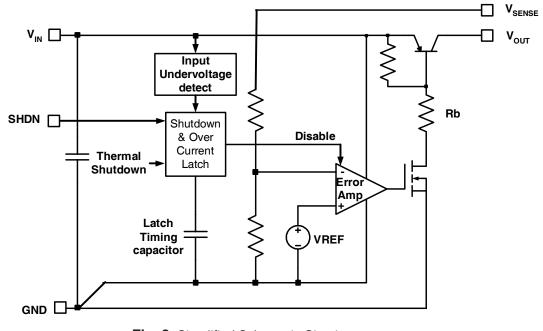

**Fig. 1.** Typical Regulator Circuit; Note the SHDN Pin is hardwired in the "ON" position. The V<sub>SENSE</sub> Pin is connected as noted in the "General Layout Rules" section.

#### **Over-Current & Over-Temperature Protection**

The IRUH3301 series provides over-current protection by means of a timed latch function. Drive current to the internal PNP pass transistor is limited by an internal resistor (Rb in Fig. 3) between the base of the transistor and the control IC drive FET. If an over-current condition forces the voltage across this resistor to exceed 0.5V (nom), the latch feature will be triggered. The time-to-latch ( $t_{LATCH}$ ) is nominally 10ms. If the over-current condition exists for less than  $t_{LATCH}$ , the latch will not be set. If the latch is set the drive current to the PNP pass transistor will be disabled. The latch will remain set until one of the following actions occur:

- 1. The SHDN Pin voltage is brought above 1.2V and then lowered below 0.8V.

- 2. The  $V_{IN}$  Pin voltage is lowered below 1.7V.

If the junction temperature of the regulator IC exceeds 140°C nominal, the thermal shutdown circuit will set the internal latch and disable the drive current to the PNP pass transistor as described above. After the junction temperature falls below a nominal 125°C, the latch can be reset using either of the actions described above.

#### **Under-Voltage Lock-Out**

The under-voltage lock-out (UVLO) function prevents operation when  $V_{IN}$  is less than 1.7V (nominal). There is a nominal 100mV hysteresis about this point.

#### Input Voltage Range

The device functions fully when  $V_{IN}$  is greater than 2.8V. It enters into under-voltage lock-out at  $V_{IN}$  < 1.7V (nominal). When 1.7V (nominal) <  $V_{IN}$  < 2.8V,  $V_{OUT}$  will track  $V_{IN}$  and overshoot may occur. A larger output capacitor should be used to slow down the  $V_{OUT}$  rise rate for slow  $V_{IN}$  ramp applications.

#### Shutdown (SHDN)

The regulator can be shutdown by applying a voltage of >1.2V to the SHDN Pin. The regulator will restart when the SHDN Pin is pulled below the shutdown threshold of 0.8V. If the remote shutdown feature is not required, the SHDN Pin should be connected to GND.

## Input Capacitance

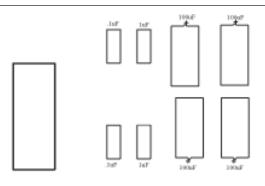

Input bypass capacitors: Two  $(0.1\mu$ F and  $1\mu$ F) ceramics and two  $100\mu$ F low ESR tantalums (AVX TPS or equivalent), placed very close to the V<sub>IN</sub> Pin are required for proper operation. When the input voltage supply capacitance is more than 4 inches from the device, additional input capacitance is recommended. Larger input capacitor values will improve ripple rejection further improving the integrity of the output voltage.

#### **Output Capacitance**

Output bypass capacitors: Two  $(0.1\mu$ F and  $1\mu$ F) ceramics and two  $100\mu$ F low ESR tantalums (AVX TPS or equivalent) are required for loop stability. Faster transient performance can be achieved with multiple additional  $1\mu$ F ceramic capacitors. Ceramic capacitors greater than  $1\mu$ F in value are not recommended as they can cause stability issues.

Tantalum capacitor values larger than the suggested value are recommended to improve the transient response under large load current changes. The upper capacitance value limit is governed by the delayed over-current latch function of the regulator and can be as much as  $10,000\mu$ F without causing the device to latch-off during start-up.

### **General Layout Rules**

Low impedance connections between the regulator output and load are essential. Solid power and ground planes are highly recommended. In those cases where the board impedances are not kept very small, oscillations can occur due to the effect of parasitic series resistance and inductance on loop bandwidth and phase margin.

The  $V_{\text{SENSE}}$  Pin must be connected directly to the  $V_{\text{OUT}}$  Pin using as short a trace as possible with the connection inside the first bypass capacitor (see Fig. 2a).

Connect ceramic output capacitors directly across the  $V_{OUT}$  and GND Pins with as wide a trace as design rules allow (see Fig. 2a). Avoid the use of vias for these capacitors and avoid loops. Fig.2 shows the ceramic capacitors tied directly to the regulator output.

The input capacitors should be connected as close a possible to the V<sub>IN</sub> Pin.

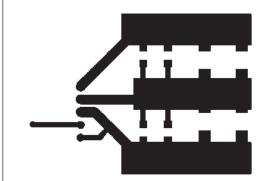

Fig. 2a. Layer 1 conductor. Ground plane below layer 1

Fig. 2b. Layer 1 silkscreen

IRUH330118BK IRUH330118BP International **ICR** Rectifier

Fig. 3. Simplified Schematic Circuit

Fig. 4. Maximum Output Current versus Mounting Surface Temperature with no Derating at Maximum Dissipation

# International **ICR** Rectifier

## IRUH330118BK IRUH330118BP

Fig. 5. Change in Output Voltage vs. Total Ionizing Dose Radiation Exposure at Both High and Low Dose Rates

**Fig. 6.** Typical Power Supply Ripple Rejection at 100mA and 1.6A using recommended layout and capacitors. Results above 10KHz are influenced by testing setup and layout.

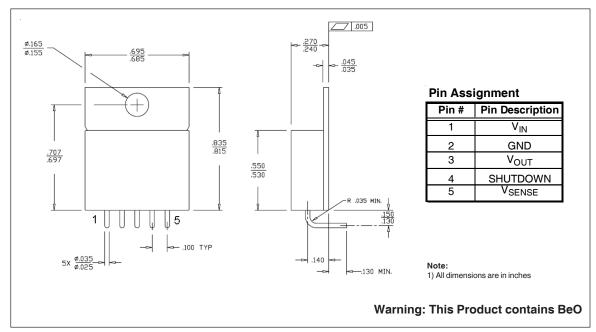

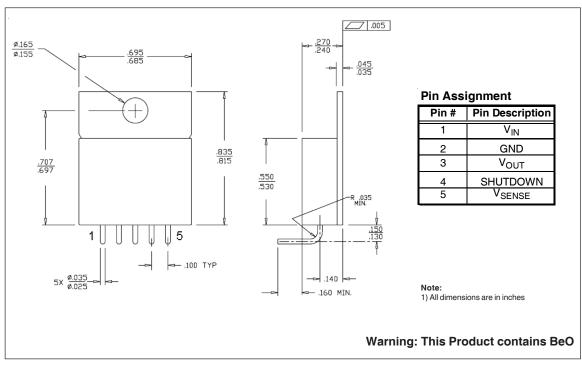

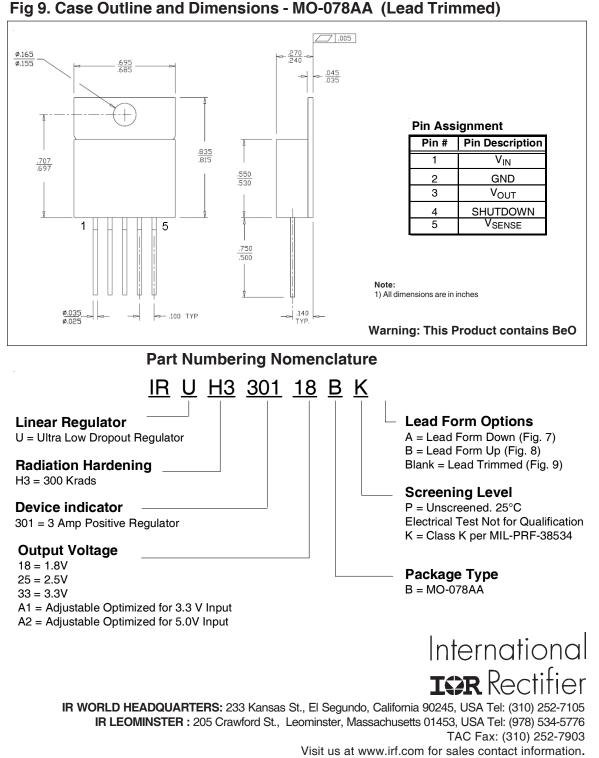

## Fig 7. Case Outline and Dimensions - MO-078AA (Lead Form Down)

International

#### IRUH330118BK IRUH330118BP

#### Data and specifications subject to change without notice. 05/2012

www.irf.com

9